当前位置:圈子 > 帖子详情

摘要

1、引言

对于当前使用的数据中心第二代供电系统而言,其电压调节器(VR,LLC谐振变换器)的电压变比高达48V:1V,未来的数据中心第三代和绿色能源互联网供电系统,其 DC/DC 变换部分(采用LLC谐振变换器)的电压变比也高达400V:12V或380V:12V[2]。无论是当前普遍使用的数据中心第二代供电系统还是未来使用的第三代和绿色能源互联网供电系统,其LLC谐振变换器都属于高电压变比结构。此外,为了满足刀片式服务器的发展趋势,LLC变换器的变压器和电感等大体积元器件必须采用低高度的平面结构和平面磁集成结构。

现有的实现LLC谐振变换器高变比的方法为在单级拓扑结构下将多个较低匝数的变压器进行磁集成[3]。传统变压器的总匝数多达40匝甚至更多[4-5],若使用PCB绕组,会导致PCB绕组的层数增加,不但绕组结构排列变得复杂,降低了可靠性,而且还极大地增加了绕组间的邻近效应和绕组损耗的分析难度。此外,采用层数较多的PCB绕组结构,不但导致PCB的制造成本很高,而且绕组导体在通过大电流时会产生较大的损耗,由损耗产生的热量很难散发出去,引起 PCB的温升过高,降低可靠性和使用寿命,使导体的电流密度受到很大限制,很难长期通过大电流,以满足服务器CPU和GPU 的低压大电流供电需求。

针对现有问题,本文提出了一种低匝比平面变压器,在保证LLC谐振变换器高变比的前提下,减少了平面变压器的绕组匝数,并且减少了磁芯元件的数量和总体积,提高了变压器效率。首先分析了高变比LLC谐振变换器主电路的工作原理和增益特性,计算出了谐振槽参数,接着给出了低匝比平面变压器磁芯的结构及其PCB绕组方案,进行了变压器的参数设计,计算其损耗和效率,搭建了变压器3D模型,进行了磁场有限元仿真,证明了该平面变压器的合理性和有效性。

2、高变比LLC谐振变换器的工作原理

2.1 高变比LLC谐振变换器的拓扑

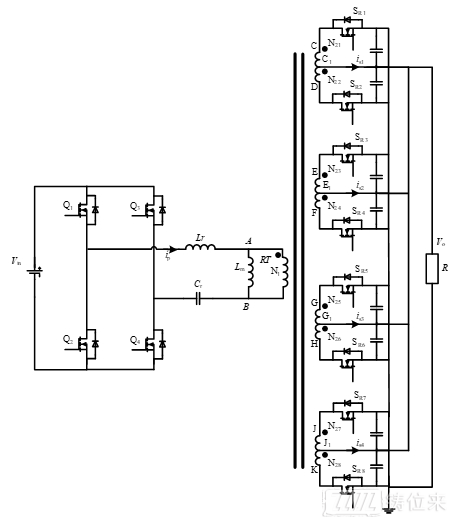

图1给出了高变比LLC谐振变换器的电路拓扑图。输入侧采用全桥结构,输出侧采用四路倍流整流电路并联,采用同步整流方式以降低导通损耗。其输入电压Vin为370V-400V DC,谐振频率fr为500kHz,输出电压Vo为12V,输出功率P为2kW。

图1 高变比LLC谐振变换器的电路拓扑图

图中,Q1-Q4为输入侧的主开关管,以50%的占空比工作,上、下开关管以180°的相位差工作。Lr为谐振电感,Lm为励磁电感,Cr为谐振电容,RT为主变压器,副边是四个含有中心抽头的变压器,SR1-SR8为输出侧的同步整流管,R为输出阻抗。

2.2 高变比LLC谐振变换器的参数计算

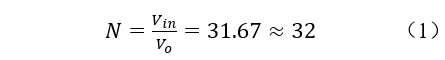

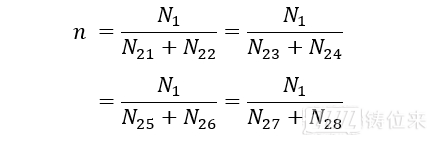

取输入电压Vin=380V,输出电压Vo=12V时,电路变比N为:

变压器的匝比n为:

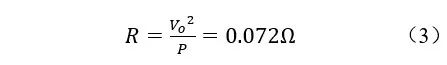

输出阻抗R为:

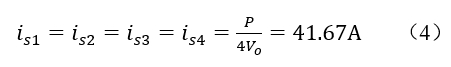

单个副边输出电流为:

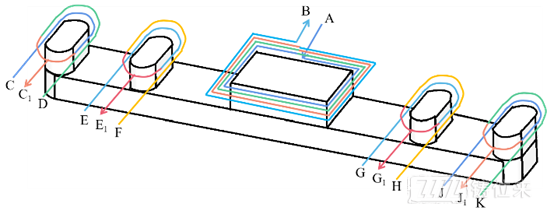

变压器副边,CC1,C1D,EE1,E1F,GG1,G1H,JJ1,J1K均只工作半个周期,即CC1,EE1,GG1,JJ1同时工作时,C1D,E1F,G1H,J1K不工作。因此其电流只有单个副边输出电流的一半。

交流等效输出电阻Rac为[6]:

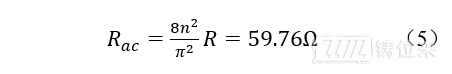

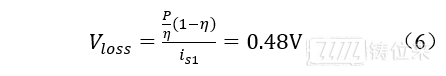

考虑到负载调整率的影响。选定实际效率η为99%,即等效输出电阻消耗了1%的功率,等效输出电阻的压降Vloss为:

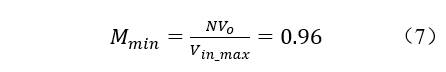

为尽可能扩大增益范围,留有裕量,在计算最小增益Mmin时,不考虑Vloss:

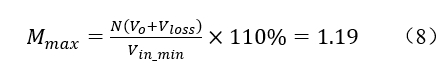

在计算最大增益Mmax时,考虑Vloss,并且保证在110%过载条件下仍然正常工作:

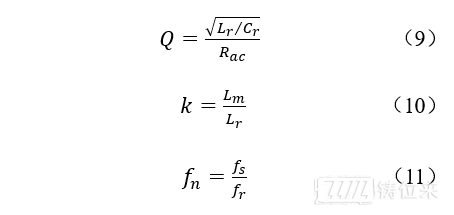

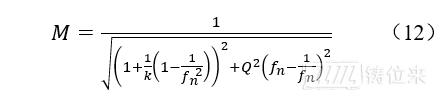

品质因数Q,电感比k,归一化频率fn的表达式[7]如下所示:

其中,fs为开关频率,fr为谐振频率。

电压增益M[8]的表达式如下所示:

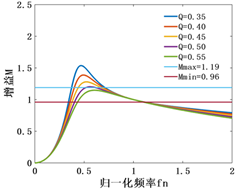

Mmax的工作点应位于并联谐振频率附近,使得系统在最低输入电压工况效率最高。k值越大,相同电压增益范围内变换器的工作频率变化范围就越大。k值越小,意味着变压器的励磁电感越小,从而使得变压器的原边电流越大,开关管和变压器的损耗越大。综合上诉因素,选取k=5。

从公式(9)可以看出,其他参数一定时,Q值与等效负载成反比,负载越重,Q值越大,增益越小。因此在设计时,只要满载时的电压增益曲线能够满足不同输入电压范围对应的增益需求即可[9]。

根据公式(12),利用Matlab绘制k值为5时,不同Q值对应的增益M和归一化频率fn的关系曲线图,如图2所示。选择Q为0.45,此时增益曲线可以达到需要的最大增益并且留有裕量。

图2 增益M曲线图

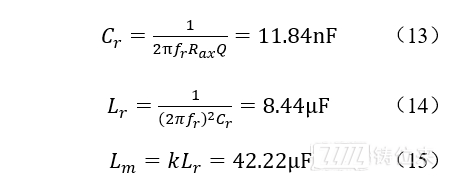

谐振槽参数计算如下:

为了减小变压器体积,取谐振槽中的谐振电感作为变压器中的漏感,谐振槽中的励磁电感为变压器的励磁电感。

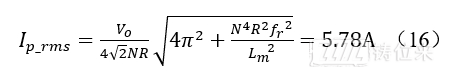

谐振电流有效值Ip_rms为:

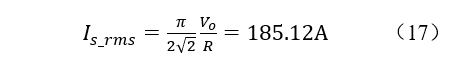

同步整流之后电流的有效值Is_rms为:

3、低匝比平面变压器设计

3.1 低匝比平面变压器磁芯设计

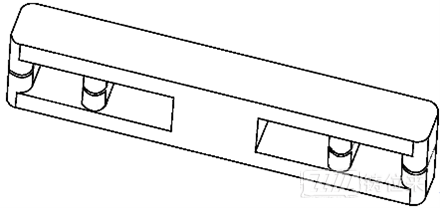

提出用于高变比LLC谐振变换器的低匝比磁芯,如图3所示。磁芯为五磁柱磁芯,四个副边磁柱采用跑道型结构在旁边,原边磁柱采用长方体在中间。四个副边磁柱的截面积之和等于原边磁柱的截面积。为保证四个副边自感及原、副边互感的一致性,将副边磁柱的气隙开到中间。为减少高频泄漏电磁场,原边磁柱不开气隙。

图3 低匝比跑道型平面变压器磁芯

根据磁导率以及磁饱和密度的需求,磁芯材料选择高频铁氧体材料DMR53,饱和磁密为0.46T,高频损耗较小,可以保证变压器在高频工作时铁芯损耗不增大。

3.2 低匝比平面变压器绕组设计

原、副边均选择PCB绕组。将图1中变压器RT的原边绕组绕在原边磁柱上,将四个带中间抽头的变压器副边绕组分别绕在四个副边磁柱上。如图4所示。

图4 低匝比跑道型平面变压器绕组缠绕方式

图4 低匝比跑道型平面变压器绕组缠绕方式

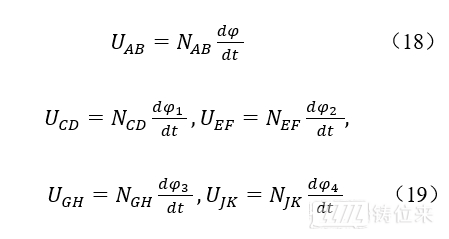

根据法拉第电磁感应定律:

式中,ψ为原边绕组AB所包围的大磁柱的磁通,ψ1、ψ2、ψ3、ψ4、分别为副边绕组CD、EF、GH、JK所包围的四个小磁柱的磁通,且四个磁通数值相等,四个小磁柱磁通的和为原边磁通。因此:

绕在每个小磁柱上的副边绕组匝数 NCD最少取2匝,以使半个副边绕组匝数NCC1、NC1D取 1 匝,则原边绕组匝数NAB取8匝,可以满足公式(2)中的变压器匝比16。满足LLC 变换器的电压变比要求,且变压器原、副边绕组总匝数为16匝,远小于传统变压器的总匝数。

原、副边均采用双面敷铜的PCB板。原边采用一个PCB绕组,每一面绕4匝绕组,副边采用4个PCB绕组,每一面绕1匝绕组。

随着温度的升高,集肤深度加深,绕组厚度以20 ℃的集肤深度作为标准:

原、副边绕组厚度均小于2倍的20 ℃下的集肤深度从而避免绕组的集肤效应。因此选择PCB敷铜为4盎司(h=0.14mm)。

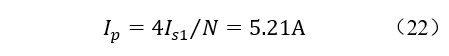

通过原边绕组的电流Ip为:

由2.1节可知,通过副边各绕组的电流Is为:

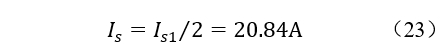

选择原边导线的宽度dp=2mm,副边导线的宽度ds=10mm,原、副边导线截面积Ap、As为:

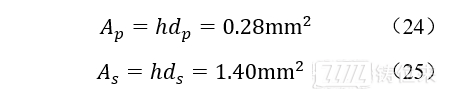

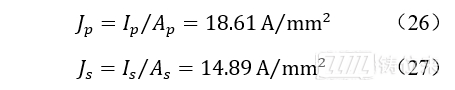

原、副边导线对应的电流密度Jp,Js为:

经计算,原、副边电流密度符合平面变压器PCB绕组的常用电流密度范围。

3.3 低匝比跑道型平面变压器损耗计算

3.3.1 铁损计算

铁损主要包括三部分:磁滞损耗、涡流损耗及剩余损耗。总的铁损可根据单位体积功率损耗Pcv进行计算:

式中,Vc为磁芯体积。

3.3.2 铜损计算

铜损分为一次侧(原边)铜损和二次侧(副边)铜损,直流电阻Rdc为:

式中,MLT为线圈平均每匝长度,N’为线圈匝数,ρw为电阻率;Aw为对应导线截面积,α20为20℃时的电阻率常数;Tmax为最高工作温度。

由于原、副边绕组厚度均小于2倍的集肤深度,可以忽略集肤效应,因此选取直流电阻和交流电阻的比值为1,即交流电阻Rac为:

铜损为:

4、低匝比跑道型平面变压器仿真

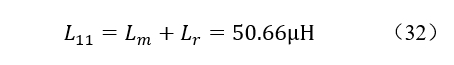

原、副边互感L12,L13,L14,L15为:

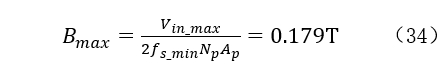

根据计算所得的原边自感和原、副边之间的互感,在ANSYS Maxwell 3D中进行所提出的低匝比平面变压器的3D模型搭建与仿真。低匝比变压器的相关建模参数如表1所示。

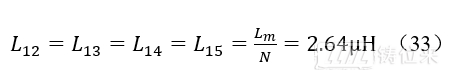

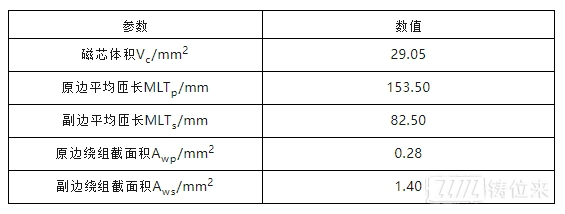

磁柱的最大工作磁密Bmax为:

对应的单位体积功率损耗Pcv为357 mW/cm3。

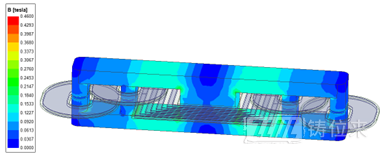

图5为低匝比平面变压器的磁通密度3D仿真结果。

图5 低匝比平面变压的磁通密度3D仿真图

图5 低匝比平面变压的磁通密度3D仿真图

整个磁芯的平均磁密为0.083T,小于0.1T,且磁密分布较为均匀。

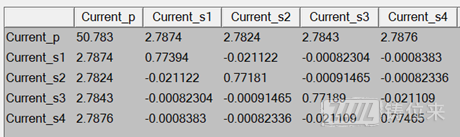

变压器的电感矩阵仿真结果如图6所示,与计算出的电感数值基本吻合。

图6 低匝比平面变压的电感矩阵仿真图

根据式(28)计算得,铁损PFe为10.88W,仿真结果为11.42W。根据式(29)-(31)计算得,铜损PCu为12.23W,仿真结果为11.17W。

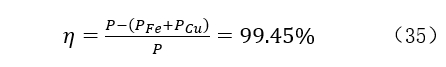

根据仿真结果进行计算,变压器效率为:

仿真得出的效率与2.2节中选定的实际效率相吻合,显著提高了变压器的效率。

5、结论

提出一种低匝比跑道型平面变压器,用于高变比LLC谐振变换器。副边四个跑道型磁柱,原边一个磁柱,原、副边绕组均采用PCB双面敷铜绕组。在实现高变比的前提下,降低了变压器匝数比,减少了磁芯原件的数量和总体积,减小了损耗,提高了效率。通过仿真验证了所提出的低匝比平面变压器的有效性和合理性。

[1]何宝宏。数据中心:下一波技术创新的制高点,信息通信技术与政策,2020年第6期:1-3页。

[2]孟明,卢玉舟,陈世超。绿色数据中心直流供电系统的 运行控制,电力建设,2016年第 37 卷,第 10 期:33-40页,2016年10月。

[3]Mohamed H. Ahmed, Chao Fei, Fred C. Lee, Qiang Li. Single-Stage High-Efficiency 48/1V Sigma Converter With Integrated Magnetic, IEEE Transactions on Industrial Electronics, VOL. 67, NO. 1, Jan. 2020.

[4]Anderson P M,Agrawal B L,Van Ness J E.Subsynchronous resonance in power system [M].New York:IEEE Press,1990.

[5]Chong-Eun Kim, Jaeil Baek, Jae-Bum Lee. Three-Switch LLC Resonant Converter for High-Efficiency Adapter With Universal Input Voltage, IEEE Transactions on Power Electronics, Vol. 36, No. 1: 630 - 638, Jan. 2021.

[6]Bo Sheng, Xiang Zhou, Wenbo Liu, ect. Adaptive Hysteresis Comparison Control of Load Sharing for Three-Phase Interleaved SCC-LLC Converter, 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 15-19 March, New Orleans, LA, USA.

[7]杨玉岗,孙彬彬,闫孝姮.考虑寄生电容的半桥LLC谐振变换器参数优化设计[J].电源学报,2019,17(02):57-62.DOI:10.13234/j.issn.2095-2805.2019.2.57.

[8]陆耀生,王勇,孔令超.基于平面变压器的LLC谐振变换器设计[J].电力电子技术,2021,55(06):125-128.

[9]童军,吴伟东,李发成,杜光辉.基于GaN器件的高频高效LLC谐振变换器[J].电工技术学报,2021,36(S2):635-643.DOI:10.19595/j.cnki.1000-6753.tces.l90259.

杨玉岗(1967),男,工学博士,教授,主要从事电力电子技术及其磁集成技术方面的研究工作。

李海潮(1997),女,硕士在读,主要从事电力电子技术及其磁集成技术方面的研究工作。

获奖公告

在上周一“本文中所提到的三种高速风筒的设计方案你更喜欢哪一种呢?你有没有什么别的不同的设计方案呢?”以及上周二“您对南京微盟电子的发展前景有何看法,会带来哪些新的机遇或挑战?”的评论互动话题中,我们收到了众多精彩的见解~

恭喜以下4位获奖的用户,前两位每人将获得价值50元以内的购书基金,后两位每人将获得1张50元京东卡的奖励!

- 查看更多打赏